DDR有望明年出世

速度在不斷飙升!AMD的AM接口 K架構處理器引入最高DDR 的支持而Intel也在月日發布了萬眾期待的Conroe處理器並進行史上規模最大的“恐怖襲擊”;電腦市場似乎在年已經提前進入了DDR 的極速時代RD支持Mhz的前端總線超頻可惜在Computex 台北電腦展上面RD似乎“臨時放棄”了DDR內存的支持轉為支持DDR 的內存所以DDR內存未能在年和觀眾們見面

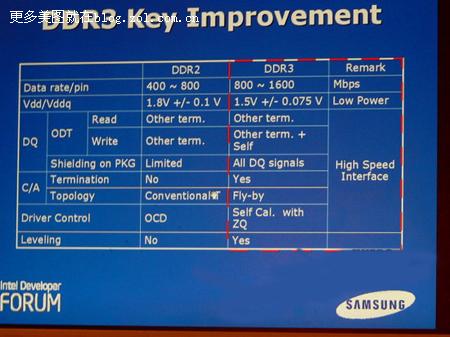

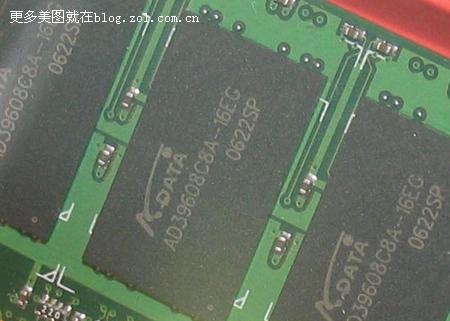

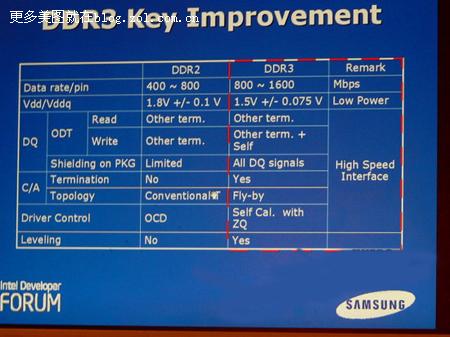

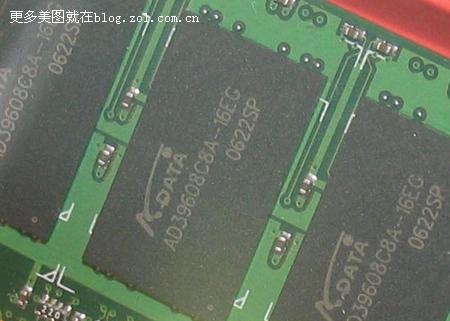

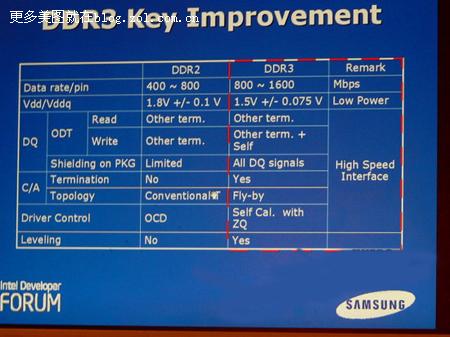

DDR相比起DDR有更低的工作電壓 從DDR的V降落到V性能更好更為省電;DDR的bit預讀升級為bit預讀DDR目前最高能夠可以達到Mhz的速度由於目前最為快速的DDR內存速度已經提升到Mhz/Mhz的速度因而首批DDR內存模組將會從Mhz的起跳在 Computex大展我們已經可以看到多個內存廠商展出Mhz的DDR模組了

DDR在DDR基礎上采用了bit預取設計;點對點的拓樸架構以及nm以下的生產工藝等最新工藝那麼DDR與DDR到底有那些不一樣的地方呢?相比DDR發燒友和玩家們可以得到哪些性能上的提升呢?

更靈活的突發長度

由於DDR的預取為bit所以突發傳輸周期也固定為而對於DDR和早期的DDR架構系統BL=也是常用的DDR為此增加了一個bit Burst Chop突發突變模式即由一個BL=的讀取操作加上一個BL=的寫入操作來合成一個BL=的數據突發傳輸屆時可通過A地址線來控制這一突發模式而且需要指出的是任何突發中斷操作都將在DDR內存中予以禁止且不予支持取而代之的是更靈活的突發傳輸控制

尋址時序提高

就像DDR從DDR轉變而來後延遲周期數增加一樣DDR的CL周期也將比DDR有所提高DDR的CL范圍一般在~之間而DDR則在 ~之間且附加延遲的設計也有所變化DDR時AL的范圍是~而DDR時AL有三種選項分別是CL和CL另外DDR 還新增加了一個時序參數“寫入延遲”這一參數將根據具體的工作頻率而定

新增重置功能

重置是DDR新增的一項重要功能並為此專門准備了一個引腳DRAM業界很早以前就要求增加這一功能如今終於在DDR上實現了這一引腳將使DDR的初始化處理變得簡單當Reset命令有效時DDR內存將停止所有操作並切換至最少量活動狀態以節約電力

在Reset期間DDR內存將關閉內在的大部分功能所有數據接收與發送器都將關閉所有內部的程序裝置將復位DLL與時鐘電路將停止工作而且不理睬數據總線上的任何動靜這樣一來將使DDR達到最節省電力的目的

新增ZQ校准功能

ZQ也是DDR一個新增的引腳在這個引腳上接有一個歐姆的低公差參考電阻這個引腳通過一個命令集通過片上校准引擎來自動校驗數據輸出驅動器導通電阻與ODT的終結電阻值

當系統發出這一指令後將用相應的時鐘周期在加電與初始化之後用個時鐘周期在退出自刷新操作後用個時鐘周期在其他情況下用個時鐘周期;對導通電阻和ODT電阻進行重新校准

電壓分成兩個和點對點連接

在DDR系統中對於內存系統工作非常重要的參考電壓信號VREF將分為兩個信號即為命令與地址信號服務的VREFCA和為數據總線服務的VREFDQ這將有效地提高系統數據總線的信噪等級

這是為了提高系統性能而進行的重要改動也是DDR與DDR的一個關鍵區別在DDR系統中一個內存控制器只與一個內存通道打交道而且這個內存通道只能有一個插槽因此內存控制器與DDR內存模組之間是點對點的關系或者是點對雙點的關系從而大大地減輕了地址/命令/控制與數據總線的負載而在內存模組方面與DDR的類別相類似也有標准DIMMSODIMM/MicroDIMMFBDIMM之分其中第二代FBDIMM 將采用規格更高的AMB高級內存緩沖器

DDR的未來一片光明

面向位構架的DDR顯然在頻率和速度上擁有更多的優勢此外由於DDR所采用的根據溫度自動自刷新局部自刷新等其它一些功能在功耗方面也比DDR要出色得多因此它可能首先受到移動設備的歡迎就像最先迎接DDR內存的不是台式機而是筆記本和服務器一樣

From:http://tw.wingwit.com/Article/Common/201311/6023.html