隨著計算機與微電子技術的發展電子設計自動化EDA(Electronic Design Automation)和可編程邏輯器件PLD(Programmable Logic Device)的發展都非常迅速熟練地利用EDA軟件進行PLD器件開發已成為電子工程師必須掌握的基本技能先進的EDA工具已經從傳統的自下而上的設計方法改變為自頂向下的設計方法以硬件描述語言HDL(Hardware Description Language)來描述系統級設計並支持系統仿真和高層綜合ASIC(Application Specific Integrated Circuit)的設計與制造電子工程師在實驗室就可以完成這都得益於PLD器件的出現及功能強大的EDA軟件的支持現在應用最廣泛的高密度PLD器件主要是現場可編程門陣列FPGA(Field Programmable Gate Array)和復雜可編程邏輯器件CPLD(Complex Programmable Logic Device)

EDA軟件方面大體可以分為兩類

① PLD器件廠商提供的EDA工具較著名的如Altera公司的 Max+plus II和Quartus IIXilinx公司的Foundation SeriesLaticeVantis公司的ispEXERT System

② 第三方專業軟件公司提供的EDA工具常用的綜合工具軟件有Synopsys公司的FPGA Compiler IIExemplar Logic公司的LeonardoSpectrumSynplicity公司的Synplify第三方工具軟件是對CPLD/FPGA生產廠家開發軟件的補充和優化如通常認為Max+plus II和Quartus II對VHDL/Verilog HDL邏輯綜合能力不強如果采用專用的HDL工具進行邏輯綜合會有效地提高綜合質量

PLD器件的開發

CPLD/FPGA設計越來越復雜使用硬件描述語言設計可編程邏輯電路已經成為大勢所趨目前最主要的硬件描述語言是VHDL(Very High Speed Integrated Circuit HDL)和Verilog HDL兩種語言都已被確定為IEEE標准

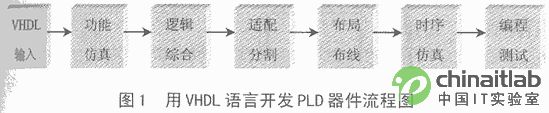

用VHDL/Verilog HDL語言開發可編程邏輯電路的完整流程為

① 文本編輯用任何文本編輯器都可以但通常在專用的HDL編輯環境中進行因為專業的集成開發環境通常提供各種結構模板並且可以自定義各種要素(例如關鍵字字符串注釋等)的色彩顯示提高可讀性提高輸入效率

② 功能仿真將文件調入HDL仿真軟件進行功能仿真檢查邏輯功能是否正確

③ 邏輯優化與綜合將源文件調入邏輯綜合軟件進行邏輯分析處理即將高層次描述(行為或數據流級描述)轉化為低層次的網表輸出(寄存器與門級描述)邏輯綜合軟件會生成EDIF(Electronic Design Interchange Format)格式的EDA工業標准文件這步在PLD開發過程中最為關鍵影響綜合質量的因素有兩個即代碼質量和綜合軟件性能

④ 適配與分割如果整個設計超出器件的宏單元或I/O單元資源可以將設計劃分到多片同系列的器件中

⑤ 裝配或布局布線將EDIF文件調入PLD廠家提供的軟件中進行裝配(對於CPLD)或布局布線(對於FPGA)即將設計好的邏輯寫入CPLD/FPGA器件中

⑥ 時序仿真即延時仿真由於不同器件不同布局布線給延時造成的影響不同因此對系統進行時序仿真檢驗設計性能消除競爭冒險是必不可少的步驟

利用VHDL語言進行PLD設計開發的基本流程如圖所示如果選用Altera公司CPLD器件作為目標器件上述過程可以在Altera公司提供的 Max+plus II或Quartus II集成開發環境中完成但如果選用專用的EDA綜合工具作為補充完成邏輯優化與綜合設計質量會更好第三方綜合軟件的主要功能就是對HDL語言的源文件進行邏輯綜合生成edf的EDA工業標准文件然後在PLD廠家提供的開發軟件中調入edf文件進行編譯仿真器件編程等過程最終完成整個設計針對Altera公司CPLD器件我們選用Quartus II + LeonardoSpectrum的EDA組合開發方式更重要的是廣大學習愛好者可以在網站免費獲得下面對兩款軟件作簡要介紹

Quartus II軟件的應用

Quartus II是Altera公司的第四代可編程邏輯器件集成開發環境提供從設計輸入到器件編程的全部功能 Quartus II可以產生並識別EDIF網表文件VHDL網表文件和Verilog HDL網表文件為其它EDA工具提供了方便的接口可以在Quartus II集成環境中自動運行其它EDA工具

利用Quartus II軟件的開發流程可概括為以下幾步設計輸入設計編譯設計定時分析設計仿真和器件編程

()設計輸入

Quartus II軟件在File菜單中提供New Project Wizard…向導引導設計者完成項目的創建當設計者需要向項目中添加新的VHDL文件時可以通過New選項選擇添加

()設計編譯

Quartus II編譯器完成的功能有檢查設計錯誤對邏輯進行綜合提取定時信息在指定的Altera系列器件中進行適配分割產生的輸出文件將用於設計仿真定時分析及器件編程

圖 LeonardoSpectrum軟件Advanced FlowTabs界面

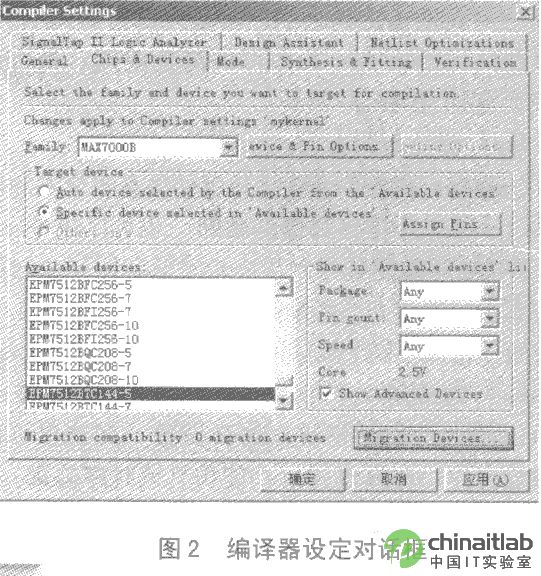

① 首先確定軟件處於Compile Mode可以通過Processing菜單進行選擇

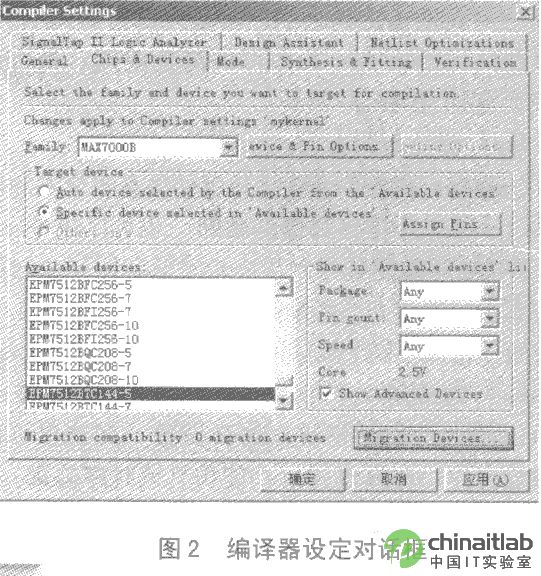

② 在Processing菜單中選擇Compiler Settings項如圖所示可以進行器件選擇模式設定綜合和適配選項設定及設計驗證等

③ 單擊Processing菜單下的Start Compilation 項開始編譯過程

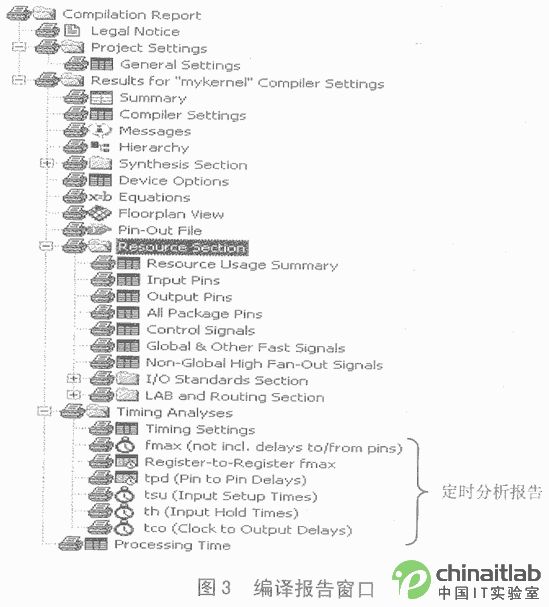

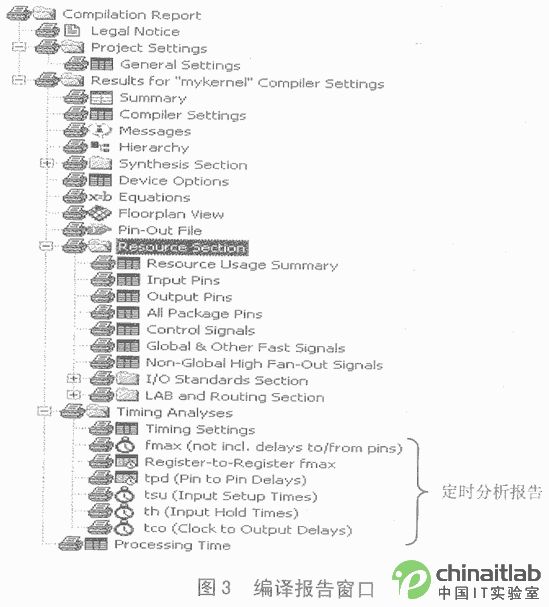

④ 查看編譯結果如圖所示我們可以得到詳細的編譯報告

()設計定時分析

單擊Project菜單下的Timing Settings…選項可以方便地完成時間參數的設定Quartus II軟件的定時分析功能在編譯過程結束之後自動運行並在編譯報告的Timing Analyses文件夾中顯示如圖所示其中我們可以得到最高頻率fmax輸入寄存器的建立時間tSU引腳到引腳延遲tPD輸出寄存器時鐘到輸出的延遲tCO和輸入保持時間tH等時間參數的詳細報告從中可以清楚地判定是否達到系統的定時要求

()設計仿真

Quartus II軟件允許設計者使用基於文本的向量文件(vec)作為仿真器的激勵也可以在Quartus II軟件的波形編輯器中產生向量波形文件(vwf)作為仿真器的激勵波形編輯方式與MAX+PLUS II軟件的操作相似在Processing菜單下選擇Simulate Mode選項進入仿真模式選擇Simulator Settings…對話框進行仿真設置在這裡可以選擇激勵文件仿真模式(功能仿真或時序仿真)等單擊Run Simulator 即開始仿真過程

()器件編程

設計者可以將配置數據通過MasterBlaster或ByteBlasterMV通信電纜下載到器件當中通過被動串行配置模式或JTAG模式對器件進行配置編程還可以在JTAG模式下給多個器件進行編程利用Quartus II軟件給器件編程或配置時首先需要打開編程器(在New菜單選項中選擇打開Chain Description File)在編程器中可以進行編程模式設置(Mode下拉框)硬件配置(Programming Hardware對話框)及編程文件選擇(Add File…按鈕)將以上配置存盤產生cdf文件其中存儲了器件的名稱器件的設計及硬件設置等編程信息當以上過程正確無誤後單擊Start按鈕即可開始對器件進行編程配置

LeonardoSpectrum軟件的應用

LeonardoSpectrum是Mentor Graphics的子公司Exemplar Logic的專業VHDL/Verilog HDL綜合軟件簡單易用可控性較強可以在LeonardoSpectrum中綜合優化並產生EDIF文件作為QuartusII的編譯輸入該軟件有三種邏輯綜合方式Synthesis Wizard(綜合向導)Quick Setup(快速完成)Advanced FlowTabs(詳細流程)方式三種方式完成的功能基本相同Synthesis Wizard方式最簡單Advanced FlowTabs方式則最全面該方式有六個選項單如圖所示分別完成以下功能器件選擇設計文件輸入約束條件指定優化選擇輸出網表文件設置及選擇調用布局布線工具

以上每步操作都提供相應的幫助簡單明了需要注意的是在輸入設計文件時要正確排列文件的次序將底層文件放在前面頂層文件放到後面這樣LeonardoSpectrum軟件才能正確地建立數據信息庫綜合完成後可以將輸出網表文件 (EDF)作為MAX+PLUS II或Quartus II的設計輸入文件再完成編譯仿真定時分析和器件編程等步驟完成整個系統的設計過程

(A)(B)(C)(D)

VHDL編碼方式對綜合質量的影響

VHDL語言支持全部的仿真功能但並不是全部可綜合的VHDL程序的許多硬件描述和仿真結構沒有對應的數字電路來實現還有些描述在理論上可以映射為對應的數字電路但是卻不能保證其精確性比如延時模型隨著綜合算法技術水平的提高針對某些寄存器傳輸級RTL(Register Transfer Level)電路描述可以進行有效的優化但是對於更普遍的電路描述這還不夠因此綜合結果是否滿足給定的時間約束條件和面積約束條件還取決於VHDL編碼方式下面給出幾點經驗相信對提高綜合質量有所幫助與啟發

()資源共享

例如下面的兩段代碼中(A)需要個加法器而完成同樣的功能略做修改(B)只需要個加法器有效地減少了使用面積

適當地利用圓括號進行重新組合有時也可以實現資源的共享如下面兩段代碼(C)和(D)(D)中輸入信號b和c即可實現加法器的共享

()使用帶范圍限制的整數

在VHDL中無約束整數的范圍是~+這意味著至少需要位來表示但通常這會造成資源的浪費有些綜合軟件會自動優化但所消耗的時間是相當可觀的因此如果不需要全范圍的整型數據最好指定范圍例如

signal small_int : integer range downto ;

small_int在本例中只需要位而不是位有效地節約了器件面積

()使用宏模塊

當在VHDL中使用算術邏輯關系邏輯等通用邏輯結構時多數EDA開發軟件及專用綜合工具通常包含針對特定工藝的優化宏模塊供我們選擇從功能上可分為時序電路宏模塊運算電路宏模塊和存儲器宏模塊具有很高的執行效率使得綜合結果面積更小頻率更高所需編譯時間更短當然它們是針對特定工藝的這將使VHDL程序依賴於具體的器件系列影響移植性

(E)(F)

()高級設計優化

上述幾種方法是在沒有改變其功能性的情況下進行綜合優化的有時候我們可以在不妨礙設計規格約束的前提下稍微改變其功能來提高綜合效率參考下面兩個例子(E)和(F)

在(E)中綜合工具建立遞增計數器和完整的比較器在(F)中綜合工具建立遞減計數器和對於常數零的比較器由於和常數作比較更易於實現且占用邏輯單元更少因此(F)程序更高效

另外由於綜合工具只能支持VHDL的子集為保證在綜合前後的仿真保持相同以下語句在綜合中應該避免使用

◇ 避免使用 wait for xx ns這種語句不會被綜合為實際的電路元件

◇ 避免使用after xx ns在綜合工具進行綜合時會忽略after語句

◇ 避免在信號和變量聲明時賦初值因為大部分綜合工具會忽略初始化語句如果使用初始化語句那麼綜合的結果和仿真的結果將會產生差異

功能強大的EDA開發軟件和專業的綜合工具的不斷發展使PLD設計或ASIC 設計過程更簡單更快捷但是要提高設計質量編程方式仍然起著至關重要的作用需要我們在實踐中不斷摸索積累經驗提高設計水平

From:http://tw.wingwit.com/Article/program/qrs/201311/11080.html